Indian Journal of Science and Technology

Year: 2022, Volume: 15, Issue: 5, Pages: 221-226

Original Article

Y G Praveen Kumar1*, B S Kariyappa2, M Z Kurian3

1Assistant Professor, Department of Electronics & Communication Engineering, Sri Siddhartha Institute of Technology, SSAHE, Maraluru, 572105, Tumakuru

2Professor & Head, Department of ECE, R V College of Engineering, Bengaluru, 560059, Karnataka

3Professor & Head, Department of ECE, Sri Siddhartha Institute of Technology, SSAHE, Maraluru, 572105, Tumakuru

*Corresponding Author

Email: [email protected]

Received Date:02 October 2021, Accepted Date:21 January 2022, Published Date:16 February 2022

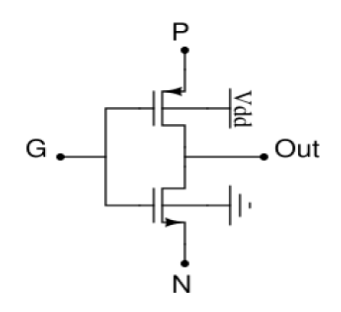

Background: A Linear Feedback Shift Register (LFSR) is typically used for generating the test patterns in built-in self-test (BIST) as it produces pseudorandom patterns at every clock cycle. These pseudo-random patterns are used as test vectors for testing the VLSI circuits. Objective: The pseudorandom patterns generated by the LFSR exhibit low-correlation among the patterns, this increases the switching activity and power dissipation while testing the VLSI circuit. Thus, to reduce the testing power, modified gate diffusion input (m-GDI) logic based LFSR in 45nm technology is proposed in this paper. Methods: The circuits are developed on m-GDI technology using the Cadence virtuoso tool and a spectre simulator is used to carry out the simulation. Findings: Comparative analysis revealed that the delay and power are reduced significantly, for the proposed design when compared to the existing LFSRs in conventional CMOS, GDI and reversible logic. Novelty and applications: In conventional LFSR, an external source is necessary to load the seed value and it dissipates more power. But in the proposed design, the seed value is generated by the circuit itself. This reduces the power and critical path delay. Further a complete zero patterns is not possible in conventional LFSR design. But in proposed design, all zero pattern is plausible. The design obtained from this study can be applied in low-power, high-speed BIST circuits.

Keywords: LFSR; Seed Value; Test Patterns; Built-In-Self-Test; m-GDI

© 2022 Kumar et al. This is an open-access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited.

Published By Indian Society for Education and Environment (iSee)

Subscribe now for latest articles and news.