Indian Journal of Science and Technology

DOI: 10.17485/IJST/v15i45.1384

Year: 2022, Volume: 15, Issue: 45, Pages: 2458-2467

Original Article

Preethi1*, K G Mohan2, Jacob Augustine3, K Sudeendra Kumar4

1Assistant Professor, Department of Computer Science and Engineering, School of Engineering, Presidency University, Rajankunte, Bengaluru, 560064, Karnataka, India

2Professor, Department of Computer Science and Engineering, GITAM University, NH-207, Nagadenehalli, Doddaballapura, 561203, Karnataka, India

3Professor, Department of Computer Science and Engineering, School of Engineering, Presidency University, Rajankunte, Bengaluru, 5600642, Karnataka, India

4Associate Professor, Department of Electronics and Communication, PES University, Banashankari, Bengaluru, 560085, Karnataka, India

*Corresponding Author

Email: [email protected]

Received Date:21 July 2022, Accepted Date:04 October 2022, Published Date:05 December 2022

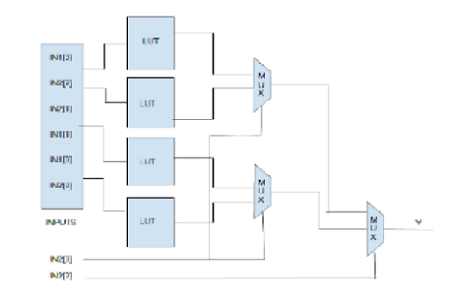

Background/Objective: Reduced Instruction Set Computer (RISC) is one of the most common types of architecture involved in microprocessor that has several blocks. There is a lot of scope that can be observed in optimizing these blocks involved in RISC resulting in better and effective microprocessors. Method: One of the sub-blocks that plays a prominent role in RISC architecture is sorter, and it can be achieved by modifying the sorting algorithm. Findings: A novel odd-even comparison-free sorting that assists in arranging N several data components in roughly N clock cycles is proposed here. N identical blocks are arranged in streamlined manner that are stacked using handful primary logic elements resulting in sorter computation. In the proposed framework, classification and categorization activities are executed in a channeled fashion. The entire design is amalgamated for numerous data sets from imitated indiscriminately generated data elements to all exceptional elements, to all the similar elements, and also from random to completely sorted data elements. It has been observed that, the algorithm appears impartial to the input ordering. Novelty: comparison-free unit was implemented on odd-even sorter. Synthesis results indicate that the proposed approach consumes reasonably low FPGA resource. The number of elements consider for sorting was N=8, this architecture takes per element sorting delay as approximately 2.1 to 4.4 ns (1 clock cycle).

Keywords: Comparisonfree technique; Hardware sorting engine; Look ip tables; RISC; Delay

© 2022 Preethi et al. This is an open-access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited. Published By Indian Society for Education and Environment (iSee)

Subscribe now for latest articles and news.