Indian Journal of Science and Technology

DOI: 10.17485/IJST/v15i23.1991

Year: 2022, Volume: 15, Issue: 23, Pages: 1143-1150

Original Article

C S Hemanth Kumar1*, B S Kariyappa2

1Assistant professor, Dept. of E&C, Government Engineering College, Ramanagara, India

2Professor, Dept. of E&C, R V College of Engineering, Bengaluru, India

*Corresponding Author

Email: [email protected]

Received Date:25 October 2021, Accepted Date:13 April 2022, Published Date:29 June 2022

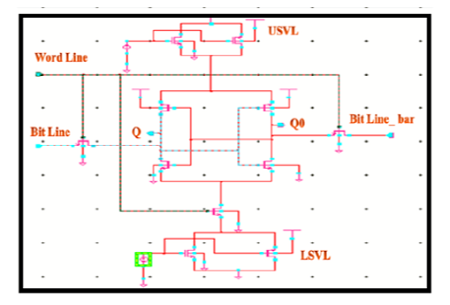

Objective: To design and propose an optimized Volatile 7T based SRAM cell in terms of leakage currents and dynamic power. Methods: The methodology involved is Multi threshold Voltage CMOS (MTCMOS), Self Controllable Voltage Level (SVL) and Improved Self Controllable Voltage Level (I-SVL). Findings: The proposed work demonstrates that 7T based SRAM cell using I-SVL method is efficient in terms of leakage currents and dynamic power. Also, Comparative Leakage current and dynamic power analyses are done between MTCMOS, SVL, and I-SVL methods The Proposed work based on I-SVL is significant than the MTCMOS and SVL Technique. All the circuits are developed using the Cadence virtuoso tool and spectre simulator is used to carry out the simulation. Novelty: The paper proposes Low power Volatile Memory cell based on 7T with improvements in leakage and dynamic power values in comparison with the earlier literatures. The proposed I-SVL based cell is 89% and 85% efficient in terms of dynamic power in comparison with the earlier references.

Keywords: Improved – Self Controllable Voltage Level (I-SVL); Improved Lower SVL (I-LSVL); Improved Upper SVL (I-USVL); Multi threshold Voltage CMOS(MTCMOS); Self Controllable Voltage Level (SVL); SRAM

© 2022 Kumar & Kariyappa. This is an open-access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited.

Published By Indian Society for Education and Environment (iSee)

Subscribe now for latest articles and news.