Indian Journal of Science and Technology

DOI: 10.17485/IJST/v14i44.1790

Year: 2021, Volume: 14, Issue: 44, Pages: 3270-3279

Review Article

S Rekha1*, K R Nataraj2, K R Rekha3, S Mallikarjunaswamy4

1Research Scholar, Department of ECE, SJB Institute of Technology, Bangalore, 560060, Karnataka, India

2Director and Dean, Don Bosco Institute of Technology, Bangalore, 560074, Karnataka, India

3Professor, SJB Institute of Technology, Bangalore, 560060, Karnataka, India

4Associate Professor, JSS Academy of Technical Education, Bangalore, 560060, Karnataka,India

*Corresponding Author

Email: [email protected]

Received Date:02 November 2021, Accepted Date:29 November 2021, Published Date:24 December 2021

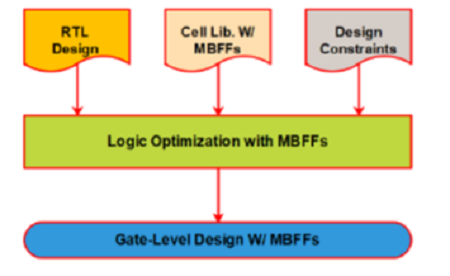

Objective: To analyze High-speed digital Integrated Circuit (IC) designing techniques and to identify the power dissipation rate in a different configuration of network switches. Methods: the complexity of a large-scale switching network is reduced using 2-bit Multi Bits Flip Flops (MBFF). The throughput and reliability are increased using a multibit flip-flop and have to be operated in parallel. The clock cycle required for 64-bit logical operation is analyzed using Xilinx software. The resources utilized during the execution process in various methods have been identified and analyzed Findings: Based on the survey, the proposed system will be built to identify characteristics of multi-bit flip flop based on switching speed (ps) concerning temperature (c), load capacity (fF), supply voltage (v), power consumption (mW) with respect to operating voltage (v) and many gates with respect to nanometer (nm) Novelty: Chip size and total power consumption rate by optimal chip reconfigurable network has been reduced to micrometer (mm) to nanometer (nm) and 0.3mW to 0.04mW respectively. Performance of parallel different applications operations in effective utilization of MBFF has been increased to 64 bits/s to 128 bits/s. The switching speed is increased with respect to clock frequency without any hazards and jitters using reconfigurable MBFF methods

Keywords: System on Chip; Multibit flipflop; multibit register; breadthfirst search; Register transfer level; Verylargescale integration

© 2021 Rekha et al. This is an open-access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited.

Published By Indian Society for Education and Environment (iSee)

Subscribe now for latest articles and news.