Indian Journal of Science and Technology

DOI: 10.17485/IJST/v14i33.1820

Year: 2021, Volume: 14, Issue: 33, Pages: 2671-2683

Original Article

Seyed E Esmaeili1*, Abeer Imdoukh2

1Assistant Professor, Engineering Department, American University of Kuwait, Safat, 13034, Salmiya, Kuwait

2Instructional Assistant, Engineering Department, American University of Kuwait, Safat, 13034, Salmiya, Kuwait

*Corresponding Author

Email: [email protected]

Received Date:06 October 2021, Accepted Date:23 September 2021, Published Date:11 October 2021

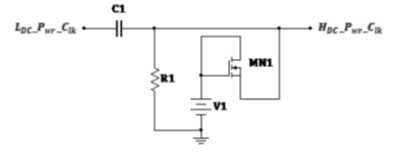

Background/Objectives: Density, performance, and design complexity of integrated circuits are rapidly increasing specifically in 3-D integration where multi-plane synchronization is required. The power and clock distribution networks consume a large portion of the limited on-chip metal resources. In order to reduce the metal overhead associated with the power, global clock, and local clock distribution networks, the concept of an integrated power and clock distribution network (IPCDN) was investigated and correct functionality of combinational and sequential elements verified. This study discusses potential power savings in IPCDNs achieved by reducing the central voltage at which the signal oscillates. Methods/Statistical analysis: In this paper, an IPCDN with differential power-clock signals centered at half the supply voltage is proposed to further reduce the power consumption. The elements of the proposed scheme including the LC differential power-clock driver, clamping circuit, clock buffer, and voltage doubler have been simulated using Tanner 0.25 um CMOS technology at a frequency of 50 MHz and a supply voltage of 2.5 V. Findings: Simulation results indicate that the proposed scheme achieves 75.32% and 76.47% power reduction in the LC differential powerclock driver and clock buffer, respectively. The effects of process, voltage supply, and temperature (PVT) variations on the proposed scheme were also investigated. Discussion: The IPCDN has a large capacitance and is heavily loaded, thus reducing the central voltage of the resonant sinusoidal signal flowing in this network enables significant reduction in power consumption. Novelty/Applications: The proposed scheme enables power reductions in the LC differential power clock driver and clock buffer. The effects of process, voltage supply, and temperature (PVT) variations on all circuit elements of the proposed scheme was investigated.

Keywords: resonant clocking; power reduction; routing complexity; LC clock driver; clock buffer; clamping circuit; voltage doubler Density, performance, and design complexity of integrated circuits are rapidly increasing specifically in 3-D integration where

multi-plane synchronization is required. The power and clock distribution

networks consume a large portion of the limited on-chip metal resources. In

order to reduce the metal overhead associated with the power, global clock,

and local clock distribution networks, the concept of an integrated power and

clock distribution network (IPCDN) was investigated and correct functionality of

combinational and sequential elements verified. This study discusses potential

power savings in IPCDNs achieved by reducing the central voltage at which

the signal oscillates. Methods/Statistical analysis: In this paper, an IPCDN

with differential power-clock signals centered at half the supply voltage is

proposed to further reduce the power consumption. The elements of the

proposed scheme including the LC differential power-clock driver, clamping

circuit, clock buffer, and voltage doubler have been simulated using Tanner

0.25 um CMOS technology at a frequency of 50 MHz and a supply voltage

of 2.5 V. Findings: Simulation results indicate that the proposed scheme

achieves 75.32% and 76.47% power reduction in the LC differential powerclock

driver and clock buffer, respectively. The effects of process, voltage

supply, and temperature (PVT) variations on the proposed scheme were also

investigated. Discussion: The IPCDN has a large capacitance and is heavily

loaded, thus reducing the central voltage of the resonant sinusoidal signal

flowing in this network enables significant reduction in power consumption.

Novelty/Applications: The proposed scheme enables power reductions in

the LC differential power clock driver and clock buffer. The effects of process,

voltage supply, and temperature (PVT) variations on all circuit elements of the

proposed scheme was investigated.

Keywords: resonant clocking; power reduction; routing complexity; LC clock

driver; clock buffer; clamping circuit; voltage doubler

© 2021 Esmaeili & Imdoukh. This is an open-access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited. Published By Indian Society for Education and Environment (iSee)

Subscribe now for latest articles and news.