Indian Journal of Science and Technology

Year: 2023, Volume: 16, Issue: 42, Pages: 3743-3755

Original Article

Sachchidanand Shukla1*, Syed Shamroz Arshad2, Pratima Soni2, Aditya Kumar Sharma2, Geetika Srivastava2

1Professor, Department of Physics and Electronics, Dr. Ram Manohar Lohia Avadh University, Ayodhya, 224001, India

2Department of Physics and Electronics, Dr. Ram Manohar Lohia Avadh University, Ayodhya, 224001, India

*Corresponding Author

Email: [email protected]

Received Date:21 April 2023, Accepted Date:25 October 2023, Published Date:12 November 2023

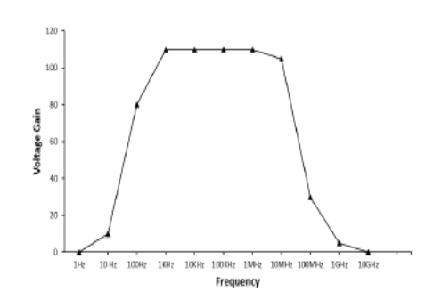

Objective: Objective of the manuscript is to introduce a novel idea of designing a small-signal common collector (emitter follower) amplifier with user-defined PSpice model of PNP Sziklai pair. Method: A circuit simulation program is developed on the PSpice simulation platform to design and study the proposed amplifier circuit. Small-signal AC equivalent circuit analysis authenticates the proposed amplifier design and selection of biasing components. The proposed amplifier is also implemented on Cadence Virtuoso Simulation software at 180nm technology to validate the design by performing its layout and post-layout simulation. Findings: The proposed circuit gives high current gain and smaller gain fluctuations (β) due to environmental parameter variations. The effect of variation in stage current gain of Sziklai pair components is observed under different operating conditions. Equivalent circuit analysis, noise performance, and the effect of temperature on the performance of the proposed circuit are widely discussed. Other possible circuit structures with a similar concept of design are also discussed as special cases. Highly stable amplifier current gain as well as device current gain, high amplifier voltage gain, device voltage gains below unity, and low harmonic distortion are prime features of proposed circuit. The problem of finding a matched pair of BJTs for the Sziklai pair is also addressed in the proposed design. The linear distortion-less operation of this circuit, combined with its very high current gain, makes it a suitable candidate for instrumentation amplifiers with wide operating frequency range. The proposed amplifier takes up (10.105 x 10.055) μm2 of area at 180nm technology. The results of pre-layout and post-layout AC responses show that there is a close resemblance between the parameters before and after the layout, which promotes the usability and design of the proposed amplifier. Novelty: The idea explored in the manuscript is entirely new and first time announced by authors.

Keywords: PNP Sziklai Pair, Common Collector Amplifier, Current Gain, Small Signal Amplifier, Cadence Virtuoso

© 2023 Shukla et al. This is an open-access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited. Published By Indian Society for Education and Environment (iSee)

Subscribe now for latest articles and news.