Indian Journal of Science and Technology

DOI: 10.17485/IJST/v15i34.1033

Year: 2022, Volume: 15, Issue: 34, Pages: 1648-1654

Original Article

Jyoti Sehgal1*, Manoj Kumar2

1Research Scholar, UIET, MDU, Rohtak, Haryana, India

2Assistant Professor, UIET, MDU, Rohtak, Haryana, India

*Corresponding Author

Email: [email protected]

Received Date:15 May 2022, Accepted Date:15 July 2022, Published Date:27 August 2022

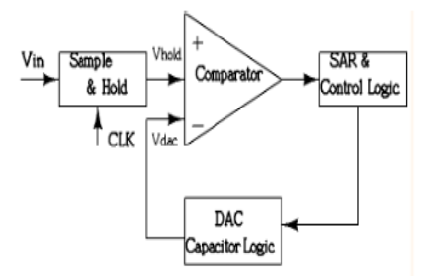

Background/Objectives: Power optimization is a critical design criterion in modern integrated circuits. The unwanted clock signals are neutralized and the reduction in power consumption is made presumable by using the clock gating technique. Methods: Analog-to-digital converters (ADCs) are important components in these systems. A widely used successive approximation register A/D converter includes an internal clock, reference, and high resolution. The number of redundant cycles is increased with improved resolutions but enhances the consumption of power. Thus, the clock gating strategy is used to substantially lower the circuit’s dynamic power consumption. The clock gating technique is implemented with a reduced number of transistors to minimize the overhead with high switching activity. Also, demonstrate no imperfection on the clock duty cycle. Findings: A 12-bit clock gated SAR register using a D-flip flop with 1.8 V supply voltage is proposed in this study for efficient biomedical applications. SAR without a clock gating technique consumes 54 mW of power and SAR with a clock gating technique consumes a power of 22.68 mW. Novelty: The clock gating technique is stipulated to minimize power consumption of clock gated SAR-ADC and improves the battery life of the portable device.

Keywords: Clock gated technique; power consumption; resolution; SARADC; successive approximation register

© 2022 Sehgal & Kumar. This is an open-access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited.

Published By Indian Society for Education and Environment (iSee)

Subscribe now for latest articles and news.