Indian Journal of Science and Technology

DOI: 10.17485/IJST/v17i14.3033

Year: 2024, Volume: 17, Issue: 14, Pages: 1381-1390

Original Article

J Prasad1*, M Vasim Babu2, M Kasiselvanathan3, K B Gurumoorthy4

1Assistant Professor (Sl.G), ECE, KPR Institute of Engineering and Technology, Coimbatore, Tamil Nadu, India

2Assistant Professor, Electronics Engineering, Madras Institute of Technology Campus, Chennai, Tamil Nadu, India

3Assistant Professor (Sl.G), ECE, Sri Ramakrishna Engineering College, Coimbatore, TamilNadu, India

4Associate Professor, ECE, KPR Institute of Engineering and Technology, Coimbatore, TamilNadu, India

*Corresponding Author

Email: [email protected]

Received Date:31 December 2023, Accepted Date:09 March 2024, Published Date:30 March 2024

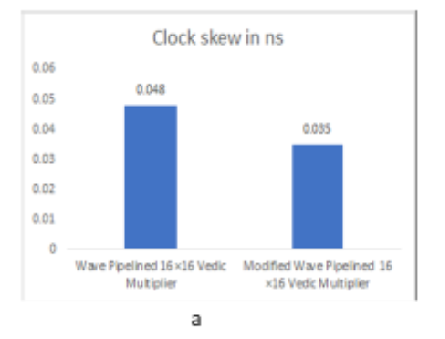

Objectives: This work objective is to construct an FPGA-based 16x16 Vedic multiplier and assess the performance of the multiplier using three distinct architectures: pipeline, wave pipeline, and modified wave pipeline in terms of delay and clock skew. Methods: The 16 × 16 Vedic multiplier was constructed and designed through four numbers of an 8x8 Vedic multiplier. For the 16x16 Vedic multiplier, the 3-stage pipeline and wave pipeline techniques are applied, and the delay performances of the Vedic multiplier are compared. Delay optimization: In the wave pipeline Vedic multiplier architecture, the delay is decreased by inserting the known delay on the longest path delay between the multiplier and adder. Clock skew optimization: The clock skew issue of the wave pipeline Vedic multiplier architecture is minimized by adjusting the setup time violation of the clock signal that is connected to the input and output registers. Findings: The delay performance of the Vedic multiplier was evaluated by the synthesis tools Xilinx 12.1, Xilinx ISE 14.2, and Altera, and based on the synthesis report, the Xilinx synthesis tool offers 73.71% delay performance for the pipeline approach and 53.39% for the wave pipeline approach compared to the Altera tool. Further delay is reduced by the proposed modified wave pipeline approach, which saves 2.122 ns of delay compared to the wave pipeline architecture. The clock skew performance was analyzed using the Time Quest timing analyzer tool, and it was minimized to 0.035 from 0.048 compared to the wave pipeline approach. Novelty: In this work, the modified wave pipeline approach has been applied to the existing Vedic multiplier architecture, and it offers less delay as well as less clock skew compared to the existing method. Hence, the performance of the Vedic multiplier with a modified wave pipelined approach was evaluated through a 3-tap FIR filter by applying a vibroarthrography signal.

Keywords: Pipeline, Wave Pipeline, Vedic Multiplier, Clock skew, Set up violation, Altera quartex- II Time quest timing analyzer tool

© 2024 Prasad et al. This is an open-access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited. Published By Indian Society for Education and Environment (iSee)

Subscribe now for latest articles and news.