Indian Journal of Science and Technology

Year: 2024, Volume: 17, Issue: 3, Pages: 247-257

Original Article

Smitha Sharath Shankar1*, S Rohith2

1Assistant Professor, Electronics and Communication Department, Nitte Meenakshi Institute of Technology, Bengaluru, Karnataka, India

2Associate Professor, Electronics And Communication Department, Nagarjuna College Of Engineering & Technology, Bengaluru, Karnataka, India

*Corresponding Author

Email: [email protected]

Received Date:30 September 2023, Accepted Date:14 December 2023, Published Date:13 January 2024

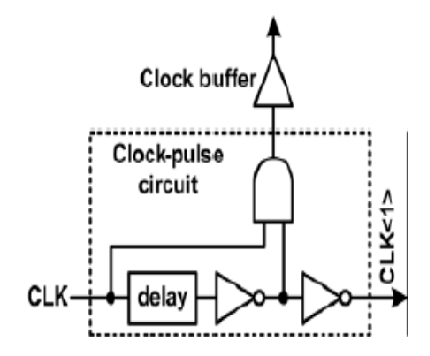

Objectives: To solve timing and power consumption issues in digital circuit design by creating a Low-Power Shift Register Based on Pulsed Latch (LPSR-PL). Targeting IoT sensors and portable devices for low-power operation, increase energy efficiency in shift registers by using numerous non-overlapping delayed pulsed clock signals, decoder-enabled design, and gated clock circuits. Methods : The work uses a unique strategy that decreases power consumption and timing difficulties by employing numerous non-overlapping delayed pulsed clock signals in the LPSR-PL. To improve data synchronisation, it combines latches into temporary store latches. The study uses a decoder-enabled design to compress control logic and simplify clock-pulse circuitry, resulting in power reductions. In addition, a gated clock circuit is designed to save energy by preventing pointless clock pulses during times of inactivity or static operation. Findings : The LPSR-PL is a good choice for contemporary digital circuit design as it efficiently addresses timing problems and reduces shift register power consumption. The employment of several non-overlapping delayed pulsed clock signals improves operating efficiency and data synchronisation. The employment of gated clock circuits, decoder-enabled architecture, and non-overlapping clock signals has led to significant advancements in low-power shift register designs. For applications where energy conservation is crucial, such as Internet of Things sensors and portable devices, this technology provides a more energy-efficient option. The suggested model performs very well with a much reduced power usage of 0.502 W. Novelty: Power consumption and timing accuracy have been problems with conventional shift registers for a very long time. Conventional methods' dependence on a single pulsed clock signal often produced inefficiencies and subpar results. The LPSR-PL, however, has altered the rules of the competition today by offering multiple non-overlapping delayed pulsed clock signals that signify a new era in digital circuits.

Keywords: Pulsed latch, Flip flop, Shift register, Xilinx ISE, Decoder

© 2024 Shankar & Rohith. This is an open-access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited. Published By Indian Society for Education and Environment (iSee)

Subscribe now for latest articles and news.