Indian Journal of Science and Technology

Year: 2021, Volume: 14, Issue: 20, Pages: 1699-1710

Original Article

Aparna✉ 1 , Ram Chandra Singh Chauhan 2

Received Date:07 March 2021, Accepted Date:16 May 2021, Published Date:11 June 2021

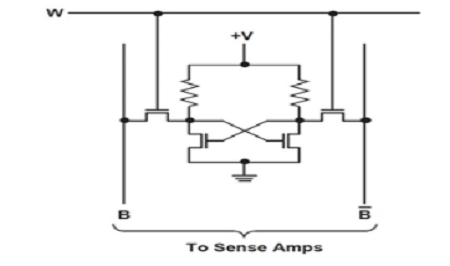

Objectives: In the present power-hungry world, the objective of this paper is to design a system that helps in the reduction of power consumption of systems. A memory cell, more specifically an SRAM cell being the major contributor to the increased power becomes an important unit to be considered in such systems for reducing power. This paper presents an improved single-ended PPN inverter based 10T SRAM cell. Methods: The proposed cell makes use of PPN-inverters. The CMOS inverter is replaced by the PPN-inverter in the conventional 8T SRAM cell giving an improved single-ended PPN-based 10T SRAM cell. Findings: The proposed work is compared with other SRAM cells based on delay, power dissipation, and power delay product (PDP). The proposed cell is designed and simulated on Cadence Virtuoso EDA tool version IC6.1.7 at a standard CMOS 45nm technology. The simulation results show that the proposed SRAM cell consumes lesser power and hence lower PDP compared to conventional 8T SRAM cell as well as other SRAM cells and with the use of high threshold voltage transistors in the read circuit a further decrease in the power consumption is observed. So, by use of PPN inverter in 8T SRAM cell a new design for low power consuming SRAM cell is achieved. Novelty: The proposed cell is optimized in terms of power dissipation making it more efficient for use in portable battery-operated devices.

Keywords

10T SRAM cell, Low power, PPN inverter, Static RandomAccess Memory (SRAM)

© 2021 Aparna & Chauhan. This is an open-access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited. Published By Indian Society for Education and Environment (iSee)

Subscribe now for latest articles and news.