Indian Journal of Science and Technology

Year: 2020, Volume: 13, Issue: 25, Pages: 2537-2546

Original Article

S.M Usha1*, H.B Mahesh2

1Associate Professor, Electronics and Communication Engineering, JSS Academy of Technical Education, Bengaluru, 560 060, Karnataka, India. Tel.: +91-990-049-9787

2Assistant Professor, Computer Science Engineering, PES University, 560085, India

*Corresponding Author

Tel:+91-990-049-9787

Email: [email protected]

Received Date:18 June 2020, Accepted Date:02 July 2020, Published Date:17 July 2020

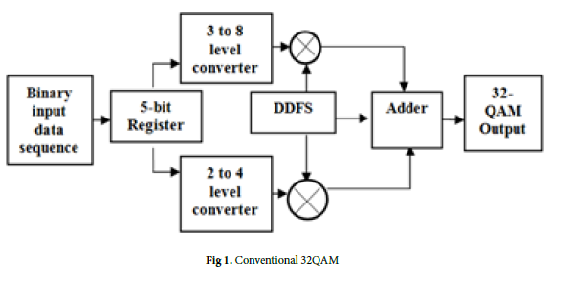

Background/Objectives: Low power modulators are most efficient for wireless communication. Quadrature Amplitude Modulation (QAM) is used widely for high data rate communication than BPSK and QPSK, since it carries more bits of information per symbol over the channel. The objective of this work is to minimize the power consumption and area utilization of 32-bit QAM modulator. Methods/Statistical analysis: In this work, three new procedures are introduced for 32QAM modulator. In the first approach, sine and cosine data generated using conventional technique are stored in ROM and the stored data is selected based on the input sequence to generate the output signal. This approach reduces the power consumption and area utilization. In the second approach, information bit stream is modulated with sine and cosine waves generated by iterative algorithm to minimize power and area requirement. In the third approach, booth multiplication algorithm is employed to generate QAM signal. This method of generating QAM signal consumes less power and area in comparison with the conventional modulator. The work is synthesized, analyzed, and compared in 180nm, 90nm and 45nm CMOS technology using Cadence software. Findings: In 180nm CMOS technology power consumption noticed is 60662.740nW, 617020.071nW and 133679.687nW with the proposed method1, method2 and method3 respectively. An Area utilized in 180nm CMOS technology is 1341mm2, 20746.757mm2, and 2754mm2 respectively in proposed 32QAM modulator with ROM, 32QAM modulator with proposed Iterative algorithm and 32QAM modulator with Booth multiplication algorithm. Novelty/Applications: The conventional 32QAM devours additional power and area. In this work area and power reduction is achieved with respect to the conventional method. The same work is carried out with 90nm and 45nm CMOS technology. Three novel approaches to 32QAM are proposed. The proposed work is synthesized, analyzed, tabulated and compared with conventional method and shown that power consumption and area utilization are minimum than compared to the conventional method.

Keywords: QAM; multiplier; power; area; communication; cadence

© 2020 Usha, Mahesh.This is an open-access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited. Published By Indian Society for Education and Environment (iSee)

Subscribe now for latest articles and news.